在最新一屆的IEEE國際電子器件會議IEDM 2024上,Intel代工技術部門公布了一系列半導體領域的突破性進展,涵蓋新材料應用、異構封裝技術、全環繞柵極(GAA)晶體管創新等多個方面。這些技術突破標志著Intel在推進其四年五個工藝節點計劃方面取得了顯著進展,旨在到2030年實現單個芯片上封裝1萬億個晶體管的目標。

其中一項引人注目的技術突破是減成法釕互連技術。該技術通過使用釕這種新型金屬化材料,并結合薄膜電阻率和空氣間隙的創新應用,成功實現了互連微縮的重大進步。這一技術的實施不僅具備量產的可行性和成本效益,還能在間距小于或等于25納米時,通過空氣間隙有效降低線間電容最高達25%,從而超越銅鑲嵌工藝的優勢。

Intel還展示了選擇性層轉移(SLT)技術,這是一種創新的異構集成解決方案,通過以更高的靈活性集成超薄芯粒,顯著縮小了芯片尺寸并提高了縱橫比。相較于傳統的芯片到晶圓鍵合技術,SLT技術能將芯片封裝中的吞吐量提升高達100倍,實現超快速的芯片間封裝。結合混合鍵合或融合鍵合工藝,SLT技術能夠封裝來自不同晶圓的芯粒,進一步提高功能密度。

在晶體管技術方面,Intel代工展示了柵極長度為6納米的硅基RibbonFET CMOS晶體管。這項技術不僅大幅縮短了柵極長度和減少了溝道厚度,還在抑制短溝道效應和提升性能方面達到了業界領先水平。這一創新為進一步縮短柵極長度奠定了堅實基礎,是摩爾定律持續發展的重要基石之一。

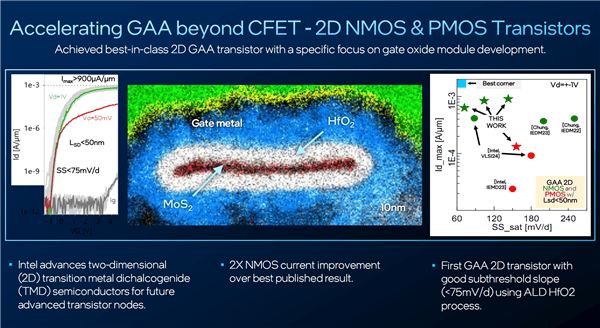

Intel還在2D GAA晶體管的柵氧化層研究方面取得了新進展。為了加速GAA技術創新,Intel展示了在2D GAA NMOS和PMOS晶體管制造方面的研究成果。該技術通過研發柵氧化層模塊,成功將晶體管的柵極長度縮小到了30納米。同時,2D TMD(過渡金屬二硫化物)研究也取得了顯著突破,未來有望在先進晶體管工藝中替代硅。

在氮化鎵(GaN)技術研究方面,Intel代工同樣取得了重要進展。在300毫米GaN-on-TRSOI(富陷阱絕緣體上硅)襯底上,Intel成功制造了高性能微縮增強型GaN MOSHEMT(金屬氧化物半導體高電子遷移率晶體管)。這一技術能夠減少信號損失,提高信號線性度,并采用基于襯底背部處理的先進集成方案。