在設(shè)計集成電路時,工程師的目標是生產(chǎn)出更容易制造的高效設(shè)計。如果他們設(shè)法降低電路尺寸,那么制造該電路的經(jīng)濟性也會下降。英偉達公司在其技術(shù)博客上發(fā)布了一項技術(shù),該公司使用一種名為PrefixRL的人工智能模型。利用深度強化學(xué)習(xí),英偉達公司使用PrefixRL模型來超越主要供應(yīng)商的傳統(tǒng)EDA(電子設(shè)計自動化)工具,如Cadence、Synopsys或Siemens/Mentor。

EDA供應(yīng)商通常會在內(nèi)部實施人工智能解決方案,以實現(xiàn)硅片放置和路由(PnR);然而,英偉達的PrefixRL解決方案似乎在該公司的工作流程中創(chuàng)造了奇跡。

創(chuàng)建一個深度強化學(xué)習(xí)模型,旨在保持與EDA PnR嘗試相同的延遲,同時實現(xiàn)更小的芯片面積,這是PrefixRL的目標。

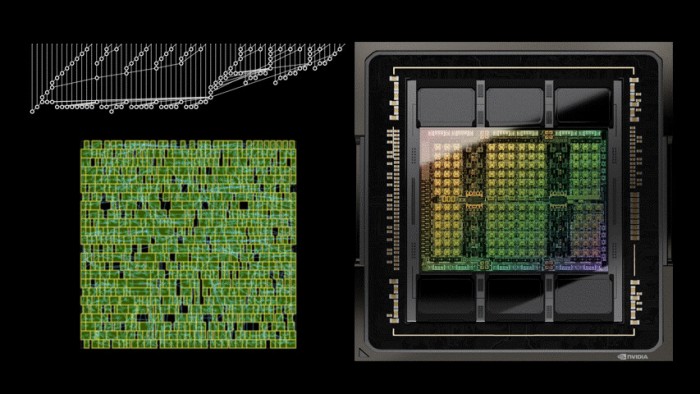

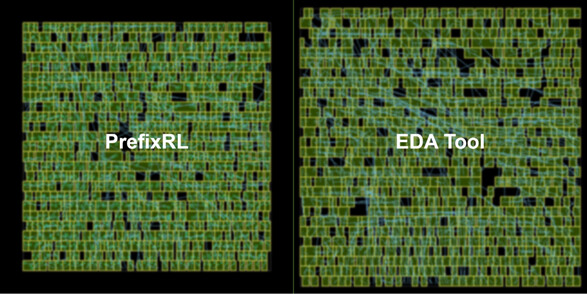

根據(jù)NVIDIA技術(shù)博客介紹,最新的Hopper H100 GPU架構(gòu)使用了PrefixRL AI模型設(shè)計的13000個算術(shù)電路實例。英偉達制作的模型輸出的電路比同類EDA輸出的電路小25%。這一切都在實現(xiàn)類似或更好的延遲。下面你可以在圖中比較PrefixRL制作的64位加法器設(shè)計和一個業(yè)界領(lǐng)先的EDA工具制作的相同設(shè)計:

訓(xùn)練這樣一個模型是一項計算密集型的任務(wù)。英偉達公司報告說,設(shè)計一個64位加法器電路的訓(xùn)練,每個GPU需要256個CPU核心和32000個GPU小時。該公司開發(fā)了Raptor,這是一個內(nèi)部分布式強化學(xué)習(xí)平臺,利用英偉達硬件的獨特優(yōu)勢進行這種工業(yè)強化學(xué)習(xí),你可以看到下面的內(nèi)容以及它的操作方式:

總的來說,該系統(tǒng)相當(dāng)復(fù)雜,需要大量的硬件和投入;然而,回報是更小、更高效的GPU。