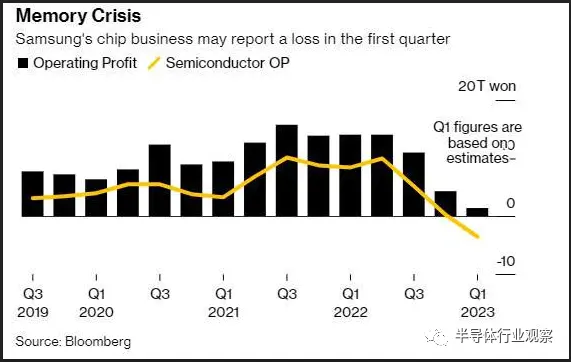

近日,三星電子披露財報數據顯示,今年第一季度實現營業利潤6000億韓元,同比降幅高達95.8%,銷售額為63萬億韓元,同比下滑19%。

這一業績也成為三星電子自2009年第一季度之后,時隔14年單季營業利潤再次跌破1萬億韓元。

在存儲芯片需求持續降溫以及業績大幅虧損的背景下,縱使“頭鐵”如三星,也終于扛不住了。由于大量庫存影響了定價和利潤,三星電子表示將把存儲芯片產量削減到“有意義的水平”。

根據三星電子3月19日提交給韓國Financial Supervisory Service的申報文件,截至2022年第四季,公司整體庫存資產達到52.2萬億韓元(近400億美元),刷新歷史新高。

SK海力士也陷入同樣的困境,根據申報文件顯示,其2022年第四季整體庫存資產攀升至15.7萬億韓元(約120億美元),同比增長75%。由于SK海力士業務主要專注于DRAM和NAND Flash,占其總營收的90%以上,因此在市況低迷時期容易受到更大打擊。

為了控制市場價格、降低庫存擠壓,SK海力士、美光科技等存儲大廠紛紛釋出減產策略。而三星電子此前一直拒絕減產,除了看好中長期市場前景之外,從競爭對手奪取市場份額也是重要原因。而如今面對多重壓力,三星電子一改此前“沒有人為減產”的基調,正式加入減產陣營。

近日也有消息透露,蘋果也在大砍M2芯片訂單、聯發科砍單超2000萬套SoC。可見,無論是終端市場的持續低迷,亦或是三星的突然轉向,或許都意味著存儲芯片的“冬天”還沒有那么快結束。

在此逆境之下,韓國存儲“雙雄”正在采取哪些措施來應對市場低迷,或者通過押注其它新技術來穿越下行周期。

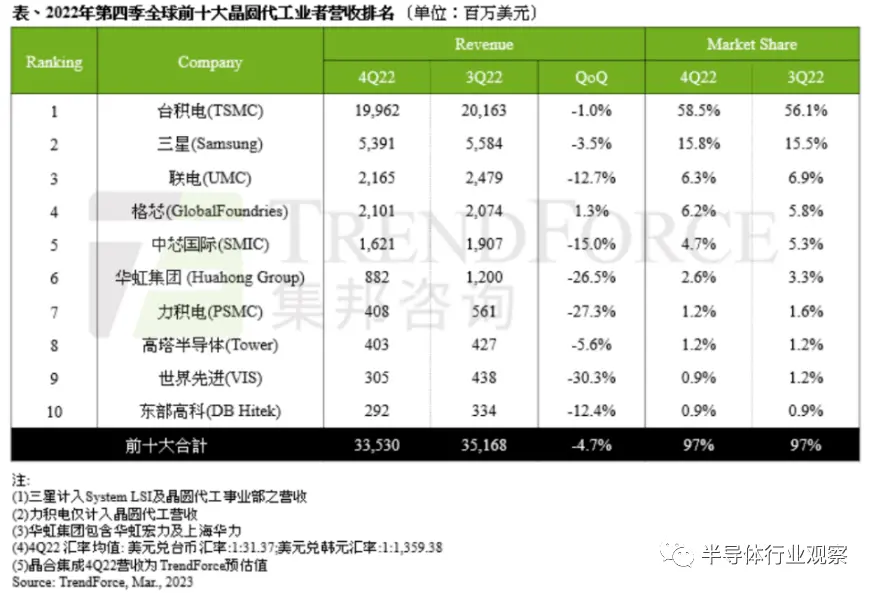

三星發力晶圓代工,追趕臺積電

近年來,在先進制程工藝上,三星和臺積電在暗自較勁。

去年6月,三星電子宣布3nm芯片量產,三星自此成為全球第一個量產3nm芯片的廠商,也是首次采用GAA工藝的芯片。

據介紹,相比5nm芯片,采用GAA工藝的3nm芯片性能將提升23%、功耗降低45%、面積縮小16%。在與臺積電的對抗中,三星先下一城,而臺積電的3nm工藝依然會采用基于FinFET的傳統工藝。

然而,雖然三星早于臺積電宣布3nm先進制程工藝的量產,不過從市場和客戶普遍反饋來看,其良率不及臺積電。良率過低會導致芯片制造成本大幅增加,這將使得三星先進工藝量產進度陷入瓶頸。

除了3nm外,三星的5nm、4nm代工良率都不高,以4nm制程為例,三星的良率僅有35%,而臺積電高達70%,大多數半導體公司不得不選擇加強與臺積電的合作關系。據悉,高通、英偉達、聯發科等廠商已預訂臺積電2023年、2024年的先進制程產能。去年底,臺積電還取代三星,成功拿下了特斯拉輔助駕駛芯片大單。

前不久,三星發布的《電子事業報告書》提到,將從2023年上半年開始大規模量產第三代4nm芯片。但一周之后,高通發布驍龍7+處理器,依舊選擇了臺積電4nm工藝。

能看到,三星電子的晶圓代工業務正在頻頻痛失大客戶。

盡管如此,三星電子依舊在此持續發力,在3nm及以下的技術上雄心勃勃。據三星電子未來技術路線圖披露,其計劃在2023年推出第二代3nm工藝,2025年開始量產2nm,進一步要在2027年推出1.4nm工藝。

產能擴張方面,3月15日,三星電子宣布計劃投資300萬億韓元(約2300億美元)在京畿道打造全球最大的半導體集群,其中將至少包含5座先進制程的晶圓代工廠,這一計劃的投資額比去年中國(含中國臺灣)半導體項目總金額還高。

三星此舉,目的在保持內存芯片霸主地位的同時,縮小在邏輯芯片上與臺積電的差距,以期在消費電子、汽車、AI等市場上獲得更高的利潤。根據三星此前公布的計劃,目標在2027年將先進制程產能較2022年提升三倍以上。

三星在晶圓代工領域的擴張,不僅體現在資金投入和擴產上,還在通過降價搶單、發力供應鏈等諸多舉措來提升自身競爭力。

有媒體報道稱,三星近日調低了晶圓代工價格,成熟制程代工報價下調10%,并已成功拿下部分臺系網通芯片廠的訂單。此舉算是掀起了行業的一大片水花,隨后聯電、世界先進等多家代工廠,也開始有條件對客戶降價。

據業界消息稱,三星代工價格原本就比同行低,所以這次降價勢必就成了一個有效的促單手段,同時對其他晶圓代工廠的影響還是很大的,要不然其他代工大廠也不可能迅速跟進。

當然,這次降價的成熟工藝。不過三星已經將目光轉向了高通和聯發科等客戶,或將進一步做出讓利,意圖從臺積電里搶回先進制程的芯片訂單。

此外,三星電子總裁暨晶圓代工事業部負責人崔世英近期在陸續指派旗下主管到訪中國臺灣,秘密接觸數家臺積電供應鏈企業,希望通過設備與材料端合作,強化三星晶圓代工良率并降低成本。

綜合來看,三星強化晶圓代工動作頻頻,不僅大力挖角臺積電人才,還在庫存調整之際大砍報價搶客,如今又有意挖臺積電設備與材料供應商墻腳,其目標相當明確,就是要拉近與臺積電的差距,同時擴大與聯電、世界先進、中芯國際等晶圓代工廠的距離,達成優化三星晶圓代工競爭力的終極戰略。

尤其是在其最重要的內存業務目前仍不見起色的關口,三星電子更需要強化晶圓代工業務,以相關獲利來支撐企業向前發展,藉此獲得更多資金來應對市況回溫。

“雙雄”押注先進封裝

隨著半導體先進工藝發展,三星電子、SK海力士正積極發展封裝技術。

三星核心短板能否補齊?

先進封裝對于晶圓代工業務越來越重要。

目前產業正在進入一個新的半導體黃金時代,這個時代的芯片制造需要從傳統晶圓代工模式思維轉變成"系統晶圓代工"。因此,先進封裝、Chiplet、生態系統和軟件都將是新代工模式的有機組成。

作為行業的佼佼者,臺積電過去因先進封裝而斬獲蘋果大單,現在更是成功整合旗下"SoIC、InFO、CoWoS"等3D IC封裝技術平臺,同時將其命名為 "3DFabric",提供業界最先進3D IC 技術,自IC的堆疊至封裝,代工服務一應俱全。

可以看出,先進封裝制程擔當"產品優化"關鍵角色,臺積電也在產業上下游垂直供應鏈中,扮演關鍵性整合角色,自前端設計至后端封裝階段,完整提供予客戶"一站式"整合服務。

欲與臺積電爭奪晶圓代工市場的三星自然也明白其中的奧妙,所以也投入大量資源進行先進封裝的開發。

去年12月,三星電子成立先進封裝(AVP)業務團隊,負責封裝技術和產品開發。三星電子表示,將以先進封裝技術超越半導體的極限。

三星電子AVP業務團隊負責人Kang Moon-soo表示:“三星電子是世界上唯一一家從事存儲器、邏輯代工和封裝業務的企業。利用這些優勢,我們將通過異構集成技術提供具有競爭力的封裝產品,例如連接最先進的邏輯半導體和EUV工藝制造的高帶寬存儲器(HBMs)等高性能存儲半導體。”

據悉,三星電子從2015年推出HBM2高帶寬存儲器開始,在2018年實現了I-Cube (2.5D)、2020年實現了X-Cube (3D)等封裝堆疊技術的創新,未來將專注于開發基于再分布層(RDL)、硅中介層/橋和硅通孔(TSV)堆疊技術的下一代2.5D和3D先進封裝解決方案。

三星電子計劃在2024年量產比普通bump處理更多數據的X-Cube (u-Bump),并在2026年推出比X-Cube (u-Bump)處理更多數據的無bump型X-Cube。

值得一提的是,三星為發展先進封裝技術,不久前挖來19年臺積電老將、臺積電前研發副處長林俊成,擔任半導體部門先進封裝事業部副總裁。雖然林俊成早已離開臺積電,但其技術履歷與臺積電的先進封裝工藝發展緊密交織在一起,他曾帶領臺積電的研發團隊建立兩大產品線:一個是CoWoS產品線,另一個是InFO/InFO-PoP,前者導入了Xilinx FPGA產品,后者則幫助臺積電贏得了蘋果A10處理器訂單。

2019年,他加入美光后,又幫助研發團隊建立了3D IC先進封裝開發產品線。此后,轉戰半導體設備廠天虹科技任執行長的幾年間,林俊成專利數也破以往記錄,為天虹的轉型發展貢獻了重要的力量。

在找來林俊成之前,三星電子還從蘋果公司找來副總裁 Kim Woo-pyung,掌管美國封裝解決中心。通過招攬人才旨在先進封裝領域急起直追,進一步顯示出三星希望在各方面都能追趕臺積電的企圖心。

近日,據臺灣電子時報消息,三星電子半導體暨裝置解決方案部門,可能從2023年第四季度起,將扇出型晶圓級封裝(FOWLP)正式導入量產,全力搶占晶圓代工關鍵制高點。

在此之前,三星就曾計劃投資韓國天安市半導體晶圓廠約2000億韓元(約1.65億美元),建立FOWLP產線,但遭到一眾高管的質疑。其反對的理由就是沒有"關鍵客戶",需求無法確保,即便建立FOWLP產線,該產線也無法被充分利用。

無論是其主要客戶、還是三星本身,對FOWLP封裝技術都不太積極。三星對其層疊封裝技術 (PoP) 擁有很大的自信,相信其有能力持續保持領先的地位。但是,當臺積電憑借FOWLP奪取了蘋果的A10處理器大單之后,三星才對FOWLP的態度出現轉變。

三星如今整合各種資源,力求在先進封裝上重奪失地。

不過,對三星能在先進封裝上走多遠,行業中仍存有很多疑慮。一方面是三星在2022年的資本支出并不高;另一方面,先進封裝事業部也是近期才分拆出來,其內部一直就有組織頻繁調整的問題,這對要長時間面對技術挑戰的團隊會帶來高度壓力,這些都使得三星在先進封裝領域面臨挑戰。

SK海力士嶄露頭角

隨著高性能半導體需求的不斷增加,半導體市場越來越意識到“封裝工藝”的重要性。順應發展潮流,SK海力士為了量產基于HBM的先進封裝產品和開發下一代封裝技術,盡力確保生產線投資與資源。

追溯SK海力士封裝技術的發展歷程,在堆疊競爭時期,SK海力士的封裝技術并未表現出顯著優勢;而隨著性能競爭時期的到來,SK海力士的封裝技術開始在市場中嶄露頭角。CoC(芯片內建芯片)技術表現尤為突出,這項技術將凸塊互聯與引線鍵合相結合,在提高運行速度和降低成本方面實現了突破。

如今,該技術已專門應用于SK海力士高密度模塊的生產和量產。SK海力士還開發了MR-MUF(批量回流模制底部填充)技術并將其應用于HBM產品中。通過這項技術確保了HBM 10萬多個微凸塊互連的優良質量。此外,該封裝技術還增加了散熱凸塊的數量,同時由于其采用具有高導熱性的模制底部填充材料,與競爭產品相比具有更加出色的散熱性能。這項技術的應用鞏固了SK海力士在HBM市場的地位,并使SK海力士在HBM3市場占據領先地位。

在如今的融合時期,SK海力士正積極發展混合鍵合(Hybrid Bonding)技術,這種技術采用Cu-to-Cu(銅-銅)鍵合替代焊接。此外,SK海力士也在研究采用Fan-out RDL(扇出型重新分配層)技術等各種封裝技術的方案。

混合鍵合技術可以進一步縮小間距,同時作為一種無間隙鍵合(Gapless Bonding)技術,在芯片堆疊時不使用焊接凸塊(Solder Bump),因此在封裝高度上更具優勢。此外,扇出型RDL技術適用于多個平臺,SK海力士計劃將該技術用于Chiplet技術為基礎的集成封裝。線間距(Line Pitch)和多層(Multi-Layer)是扇出型技術的關鍵組成部分,SK海力士計劃到2025年將確保1微米以下或亞微米(Sub-micron)級水平的RDL技術。

HBM:2023年為數不多的市場機會

另一方面,隨著ChatGPT大火,三星、SK海力士兩家內存廠商接到了越來越多的HBM訂單。

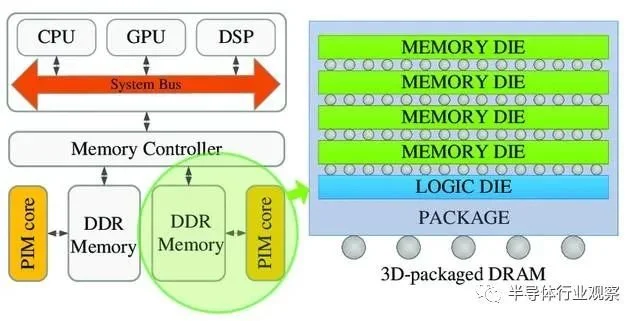

HBM(High Bandwidth Memory,高帶寬存儲器)技術可以說是DRAM從傳統2D向立體3D發展的主要代表產品,開啟了DRAM 3D化道路。

HBM主要是通過硅通孔(TSV)技術進行芯片堆疊,以增加吞吐量并克服單一封裝內帶寬的限制,將數個DRAM裸片垂直堆疊,裸片之間用TVS技術連接。從技術角度看,HBM充分利用空間、縮小面積,正契合半導體行業小型化、集成化的發展趨勢,并且突破了內存容量與帶寬瓶頸,被視為新一代DRAM解決方案。

與其他DRAM相比,HBM通過垂直連接多個DRAM顯著提高了數據處理速度。它們與CPU、GPU協同工作,可以極大地提高服務器的學習和計算性能。

目前SK海力士在HBM內存市場上占據最大的優勢,其早在2013年就跟AMD合作開發了HBM內存,整體市場份額在60-70%之間。英偉達在近日完成了對SK海力士HBM3樣品的性能評估,SK海力士將向英偉達系統供應HBM3,而該系統預計將在今年第三季度開始出貨。英特爾也在努力銷售搭載SK海力士HBM的產品。

一位業內人士表示,“與最高性能的DRAM相比,HBM3的價格上漲了5倍。”

而近年來三星也加大了HBM內存的投入,還跟AMD合作首發了HBM-PIM技術,將HBM內存與AI處理器集成在一起,大幅提高性能。因此,HBM內存將成為2023年為數不多的細分市場機會。

隨著高性能存儲半導體市場有望快速增長,三星電子和SK海力士之間的產品開發競爭正在升溫。

有關HBM的更多分析內容,見筆者此前文章《存儲巨頭競逐HBM》。

存內計算(PIM)正在成為新趨勢

存內計算(PIM)是一項打破傳統馮諾依曼架構的新型運算架構,通過將存儲和計算有機結合,直接利用存儲單元進行計算,極大地消除了數據搬移帶來的開銷,解決了傳統芯片在運行人工智能算法上的“存儲墻”與“功耗墻”問題,可以數十倍甚至百倍地提高人工智能運算效率,降低成本。

雖然存內計算的基本概念早在上個世紀七十年代就已經被提出,但直到近些年才逐漸成為人們關注的焦點,原因在于,算力和運算數據量的激增導致存儲墻問題愈發凸顯,想要進一步提高算力,只有解決存儲墻問題,而在各種解決方案中存內計算是最直接的一種方式,可以實現高能效、低功耗、低成本。

今年2月,SK海力士宣布已開發出具備計算功能的下一代內存半導體技術,隨著PIM技術的不斷發展,SK海力士期待存儲半導體在智能手機等ICT產品發揮更為核心的作用,甚至在未來成功實現“存儲器中心計算(Memory Centric Computing)”。

SK海力士還開發出了公司首款基于PIM技術的產品——GDDR6-AiM(內存加速器)的樣本。GDDR6-AiM是將計算功能添加到數據傳輸速度為16Gbps的GDDR6內存的產品。與傳統DRAM相比,將GDDR6-AiM與CPU、GPU相結合的系統可在特定計算環境中將演算速度提高至最高16倍。GDDR6-AiM有望在機器學習、高性能計算、大數據計算和存儲等領域有廣泛應用。

此外,SK海力士還計劃與最近剛從SK電訊拆分出來的人工智能半導體公司SAPEON攜手合作,推出將GDDR6-AiM和人工智能半導體相結合的技術。針對相關計算特性進行優化的演算技術的需求也在日益增加的趨勢,在數據計算、成本和能耗方面最大限度地提高效率。

實際上,SK海力士還不是最早將PIM技術應用在產品中的,早在去年2月份,三星就推出了業界首款HBM-PIM,將AI處理效能注入三星HBM2 Aquabolt,以強化超級電腦與AI應用的高速數據處理。經過測試,HBM-PIM可推升2.5倍系統效能,且降低逾60%的能耗。

三星表示,HBM-PIM測試結果展現龐大的商業潛力,隨著技術發展標準化,技術應用將進一步擴大范圍,并延伸至新世代電腦,AI應用HBM3、智能終端移動存儲及數據中心存儲模組。

存算一體仍舊是解決存儲墻和功耗墻問題的重要技術,一些處于行業領先地位的半導體公司正在積極進行自研。隨著AI的發展數據量暴增,存儲墻、功耗墻成為越來越不容忽視的問題,存內計算已然成為新趨勢。

DRAM,追逐先進制程

對DRAM芯片而言,先進制程意味著高能效與高容量,以及更好的終端使用體驗。當前,DRAM先進制程工藝——10nm級別,經歷了1x、1y、1z與1α四代技術,目前來到了第五代。

三星預計將在2023年進入1βnm工藝階段

在去年10月召開的Samsung Foundry Forum 2022活動上,三星對外公布了DRAM技術路線圖。按照規劃,三星將于2023年進入1βnm工藝階段,即第五代10nm級別DRAM產品,芯片容量將達到 24Gb(3GB)- 32Gb(4GB),原生速度將在 6.4-7.2Gbps。

為了克服DRAM擴展到10nm范圍以外的挑戰,三星一直在開發圖案化、材料和架構方面的顛覆性解決方案,高K材料等技術正在順利進行中。

此外,三星還計劃2026年推出DDR6內存,2027年實現原生10Gbps的速度。與此同時,三星新一代GDDR7顯存將在明年問世。

SK海力士——全球第一個正式發布DDR5的廠商,SK海力士還計劃今年初開始將1α納米級工藝導入全球首款DDR5 DRAM。

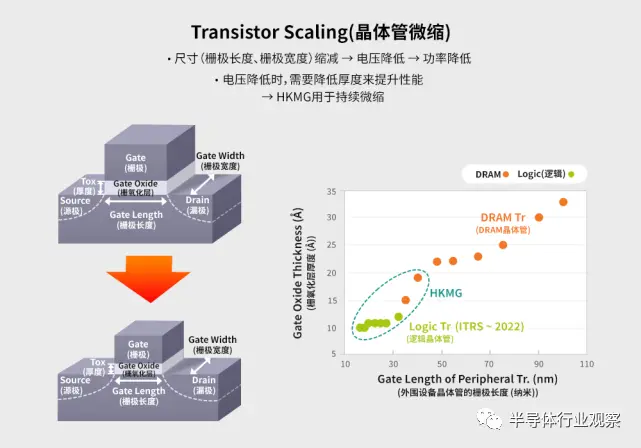

SK海力士引領High-k/Metal Gate工藝變革

由于傳統微縮技術系統的限制,DRAM的性能被要求不斷提高,而HKMG則成為突破這一困局的解決方案。SK海力士通過采用該新技術,并將其應用于全新的1anm LPDDR5X DRAM, 即便在低功率設置下也實現了晶體管性能的顯著提高。

Transistor Scaling(晶體管微縮)

在DRAM中采用高k/金屬柵極(HKMG)技術,這促使邏輯晶體管技術實現了最重大的創新。

借助HKMG,一層薄薄的高k薄膜可取代晶體管柵極中現有的SiON柵氧化層,以防止泄漏電流和可靠性降低。此外,通過減小厚度,可以實現持續微縮,從而顯著減少泄漏,并改善基于多晶硅/SiON的晶體管的速度特性。

SK海力士通過將HKMG工藝整合為適用于DRAM工藝的形式,進行了平臺開發。盡管面臨極端的技術挑戰,但公司通過識別與DRAM流相互作用相關的任何潛在風險,并通過包括試點操作在內的預驗證工藝來確保解決方案,成功開發和批量生產HKMG。SK海力士目標是通過推進從SiON/Poly柵極到升級構件HKMG的過渡,為下一代技術節點和產品帶來卓越的技術創新。

近期在HBM、PIM、AiM等邏輯半導體架構和存儲器半導體架構之間的融合上呈現出技術創新之勢,而HKMG工藝在DRAM中的應用正契合了這一趨勢。這表明,在半導體制造過程中,邏輯半導體的先進技術解決方案與DRAM工藝技術之間的融合正在全面展開。

閃存,向300層邁進

自三星2013年推出全球首款3D NAND閃存之后,閃存層數與架構不斷突破,容量也不斷提升。目前可以量產的NAND Flash最高層數已經達到了200+層,未來閃存廠商還將朝著300層甚至更高層數邁進。

去年11月,三星宣布已開始量產三星產品中具有最高存儲密度的1Tb三級單元(TLC)第8代V-NAND,其I/O速度高達2.4 Gbps,相比上一代提升了1.2倍,這可以滿足PCIe 4.0和更高版本PCIe 5.0的性能要求。

業界透露,三星第8代V-NAND層數達到了236層。此外,三星還計劃到2030年推出超過1000層的產品,以更好地支持未來的數據密集型技術。

SK海力士:300層第8代3D NAND閃存。

2022年8月,SK海力士宣布成功研發238層512Gb TLC 4D NAND閃存,計劃在2023年上半年正式投入量產。238層NAND閃存成功堆棧更高層數的同時,實現了業界最小的面積。

近日,SK海力士在ISSCC 2023會議上公布了在3D NAND閃存開發方面的最新突破。SK海力士表示,一支由35名工程師組成的團隊為這次演示的材料做出了貢獻,帶來了一款堆疊層數超過300層的新型3D NAND閃存原型。

據SK海力士介紹,第8代3D NAND閃存主要運用了五個方面的技術,包括引入三重驗編程(TPGM)功能,可縮小電池閾值電壓分布,將tPROG減少10%,從而提高性能;自適應未選字符串預充電(AUSP),另一種將tPROG降低約2%的方法;編程虛擬串(PDS)技術,降低通道電容負載來縮短tPROG和tR的世界線建立時間;平面級讀取重試(PLRR)功能,允許在不終止其他平面的情況下改變平面的讀取級別,從而立即發出后續讀取命令,最終提高了服務質量和讀取性能。

SK海力士沒有提供第8代3D NAND閃存的時間表,有行業人士估計,可能要等到2024年末或2025年某個時候才會上市。與此同時,SK海力士的第7代238層3D NAND閃存預計將被整合到2023年推出的新款閃存產品的生產周期里。

寫在最后

盡管半導體產業發展暫時進入“寒冬”,但從韓國存儲“雙雄”的動態和布局來看,存儲賽道上的技術競爭仍舊十分激烈。

無論是第五代10nm級DRAM技術,還是更高層數堆疊的NAND Flash,以及HBM、PIM等創新技術,存儲大廠都在積極發力,以保持市場領先地位,并滿足市場對高容量、高性能產品需求,呈現出持續發展的潛能。

與此同時,三星和SK海力士也在加大對晶元代工市場和先進封裝領域的布局,通過押注其它賽道來應對存儲市場的持續低迷。

【來源:半導體行業觀察】