【ITBEAR科技資訊】5月26日消息,據韓國媒體The Elec報道,三星公司近日成立了一支專業團隊,致力于開發一種名為4F2 DRAM存儲單元結構的創新技術。這項技術可以在不改變工藝節點的前提下,將芯片面積最高減少30%。

過去的十年里,DRAM行業曾嘗試商業化4F Square單元結構技術,但未能取得成功。然而,三星此次組建的專業團隊力求克服之前的難題,推動4F2結構的研發。

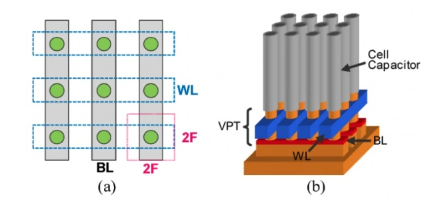

據ITBEAR科技資訊了解,4F2 DRAM存儲單元結構的設計基于晶體管形成的源極(S)、柵極(G)和漏極(D)整套系統。在漏極(D)的上方安裝了一個用于存儲電荷的電容器,并且晶體管與水平排列的WL線和垂直排列的BL線相連。其中,WL線與柵極(G)相連,負責控制晶體管的開關;而BL線與源極(S)相連,負責讀取和寫入數據。

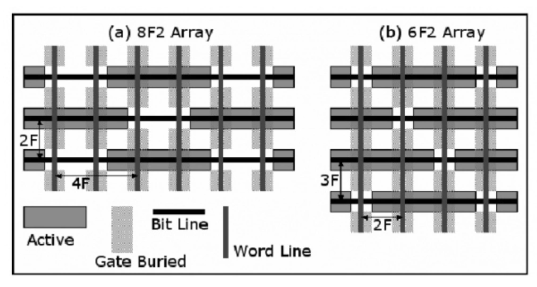

這項4F2技術的最大優勢在于其高度集成化和節省芯片空間的能力。相較于現有的6F2級別,該技術可在不改變工藝節點的情況下,將芯片面積最高減少30%。這對于提升芯片性能、實現更高容量的存儲器以及滿足不斷增長的市場需求具有重要意義。

三星公司的專業團隊將繼續努力,加快4F2 DRAM存儲單元結構的研發進程。一旦成功商業化,這項技術有望為DRAM行業帶來革命性的突破,推動存儲器技術的發展邁上新的臺階。我們將持續關注這一領域的最新動態。