隨著網(wǎng)絡通信技術的發(fā)展,芯片在軍事、經(jīng)濟和社會中發(fā)揮著越來越重要的作用。分組密碼[1]作為重要的加密算法,其高效實現(xiàn)直接影響系統(tǒng)的性能。可重構陣列密碼處理器針對不同的加密算法進行優(yōu)化,相比ASIC專用處理器,具有很高靈活性。近年來,面向分組密碼可重構處理架構的研究也越來越多。因此,如何充分開發(fā)分組密碼的并行性[2]和流水特性[3],如何設計高性能可重構分組密碼處理架構,已經(jīng)成為密碼實現(xiàn)技術的重要研究問題之一。

國內(nèi)外的研究者們對可重構分組密碼的高效實現(xiàn)進行了研究。文獻[4]提出了含有多Bank存儲器的新型CGRA架構,數(shù)據(jù)被存儲在多個Bank內(nèi),雖然提高了并行訪問能力,但由于和本文需要處理的粗粒度位寬不匹配,因此未能充分達到并行的需求。文獻[5]提出了可重構分簇式分組密碼處理架構RCBCP,設計并實現(xiàn)了5級及運算單元內(nèi)流水結構,提高了分組算法的加密性能。但復雜的可重構運算單元,使得關鍵路徑較大,在一定程度上限制了系統(tǒng)的性能。文獻[6]提出的Cryptoraptor陣列結構處理器,集成了80個PE處理單元,使得和DES算法在CBC模式下的吞吐率達到6.4 Gb/s和2.67 Gb/s,資源消耗巨大。

為充分挖掘分組密碼的并行性和流水特性,本文首先提出了一種可重構多發(fā)射流水處理架構(Reconfigurable Multi-launch Pipeline Processing Architecture,RMPA)。設計該架構的目的在于減少閑置資源,從而提高可重構計算處理器的資源利用率和運算效率。此外,為了滿足可重構陣列系統(tǒng)的高并行度特點,本文還提出了相應的多發(fā)射數(shù)據(jù)管理機制。高效的數(shù)據(jù)管理對于可重構陣列的處理性能有顯著的提升。

1 RMPA-可重構多發(fā)射流水處理架構

可重構分組密碼多發(fā)射流水處理架構RMPA是以PEs陣列為主要構成元素,結合流水線技術提出的。流水線結構是高效計算常采用的處理結構。通過分析分組密碼的核心操作,并用流水結構進行處理,使得多個數(shù)據(jù)在流水線中并行開始不同的操作。該架構的基本思路是:利用具有32 bit粗粒度的n×n-PEs陣列來處理各種粒度的密碼算法,并從中開發(fā)算法的深度流水和適度并行特性。

1.1 RMPA整體架構設計

RMPA整體架構如圖1所示,可抽象分成3級:RU(Reconfigurable Unit)功能單元級、RE(Reconfigurable Element)陣列級和RMPA架構級。RU功能單元是提供密碼操作功能的關鍵部件,在詳細分析了分組密碼算法運算單元的基礎上,RU功能單元主要執(zhí)行以下7種操作:S盒、GF(2n)乘法、移位、模乘、比特置換、邏輯和模加/減。每一個RU可以執(zhí)行一個字級操作,能夠滿足分組密碼的各種位寬,并且每個RE都附加了一個寄存器文件(Register file)和一個配置寄存器(Configuration Reg),寄存器文件用于寄存臨時數(shù)據(jù)和中間結果。配置寄存器通過配置不同上下文,可以提高系統(tǒng)的處理性能。PE陣列是由n×n個REs通過Crossbar分層互連結構組成的。RMPA架構主要由主控制器(Main Controller)、配置上下文控制器(Context Controller)、RE陣列(Array)、主存儲器(Main Memory)、Bank存儲器(Bank Memory)和密鑰存儲器(Key Memory)構成。主控制器負責對整個系統(tǒng)進行控制。主存儲器存儲配置信息和數(shù)據(jù),它會根據(jù)需求將數(shù)據(jù)輸入到配置模塊或Bank存儲器中。Bank存儲器則是存儲待處理的數(shù)據(jù)和處理完的數(shù)據(jù),且Bank存儲器可以被RE陣列和DMA控制器訪問,DMA控制器負責主存儲器和Bank存儲器之間進行數(shù)據(jù)交換。密鑰存儲器用于存儲算法生成的子密鑰。該結構采用動態(tài)模式配置上下文,每一個RE內(nèi)部都有自己的配置寄存器,而且能夠直接和配置上下文存儲器連接。配置控制器從本地配置存儲器選擇正確的上下文,然后寫進每一個REs的配置寄存器。

1.2 多總線互連網(wǎng)絡結構

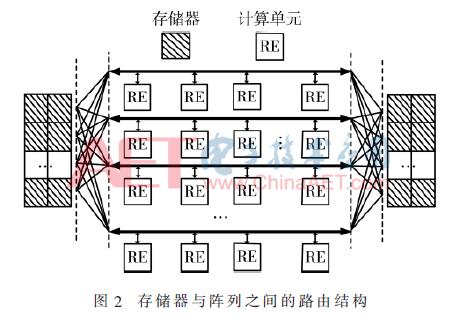

陣列中處理單元的行與列之間多采用總線、2D-Mesh和Crossbar互連結構。相比之下,雖然總線和2D-Mesh的代價較低,但在靈活性上與Crossbar相差甚遠。為使并行處理更加高效地進行,同時降低互連網(wǎng)絡的復雜度,本文在Crossbar網(wǎng)絡的基礎上采用多總線互連網(wǎng)絡結構。

Bank存儲器與陣列之間采用多總線互連網(wǎng)絡結構,如圖2所示。同一列上的RE需連接到一條總線上,任一列的總線可以連接到任何一個Bank上,這種互連網(wǎng)絡能夠保證每一個PE可以訪問到任何一個Bank,任何一個Bank內(nèi)的數(shù)據(jù)可以輸入到功能單元中;每一層的數(shù)據(jù)可以進行隔層傳輸,處理完的數(shù)據(jù)或輸出到Bank存儲器或密鑰存儲器內(nèi)。這種互連網(wǎng)絡結構使該架構能夠靈活支持CBC反饋模式的密碼運算。

2 RMPA架構多發(fā)射機制

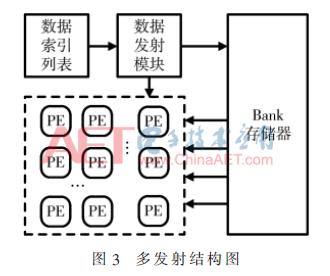

RMPA架構的多發(fā)射機制,原理就是使存儲器往陣列中同時發(fā)射多組數(shù)據(jù),進而有效提高系統(tǒng)的處理性能。為滿足這一條件,不僅需要設計一種數(shù)據(jù)多發(fā)射結構,而且對存放數(shù)據(jù)的Bank也有一定的要求。多發(fā)射結構如圖3所示,主要由數(shù)據(jù)分發(fā)模塊和數(shù)據(jù)索引列表組成。數(shù)據(jù)分發(fā)模塊的作用在于確保可重構陣列中數(shù)據(jù)的流水實現(xiàn);數(shù)據(jù)索引列表則對數(shù)據(jù)包進行區(qū)分,以保障數(shù)據(jù)包的完整性。

2.1 RAM存儲結構

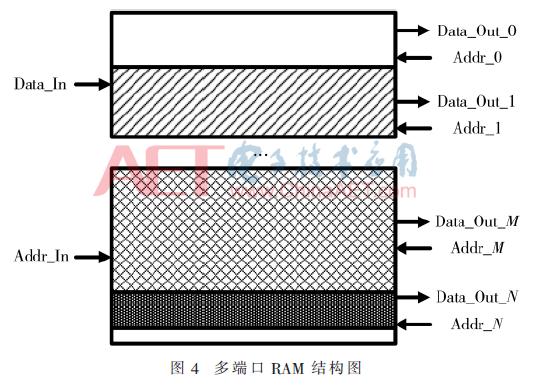

基于多發(fā)射研究,考慮如何實現(xiàn)數(shù)據(jù)包存儲資源的動態(tài)分配[7],從而降低硬件資源的浪費和吞吐率的提升。RAM作為重要的Bank組成結構,主要用于實現(xiàn)對數(shù)據(jù)的緩存,不同于FIFO結構的數(shù)據(jù)輸入輸出過程,RAM依靠地址實現(xiàn)對數(shù)據(jù)的寫入與讀出,數(shù)據(jù)讀出順序與其寫入順序無關。因此,構建了圖4所示的多端口RAM結構。

采用多輸出RAM結構構建了數(shù)據(jù)存儲的基礎,通過地址選擇輸出數(shù)據(jù)的來源。由于RAM地址是連續(xù)的,因此在數(shù)據(jù)存儲時可以確保數(shù)據(jù)的連續(xù)存儲,通過地址來區(qū)分不同的數(shù)據(jù)包,使數(shù)據(jù)包的注入更加靈活。為了滿足對不同長度數(shù)據(jù)包的并行注入及下一數(shù)據(jù)包的動態(tài)加載,下面將針對數(shù)據(jù)發(fā)射模塊的結構展開詳細研究。

2.2 數(shù)據(jù)發(fā)射模塊結構及索引列表

數(shù)據(jù)發(fā)射模塊是確保可重構陣列流水實現(xiàn)的基礎,根據(jù)上一節(jié)對數(shù)據(jù)存儲模塊的研究可知,數(shù)據(jù)存儲模塊采用多輸出RAM結構實現(xiàn)。同時,由于不同數(shù)據(jù)包的長度不同,因此數(shù)據(jù)發(fā)射模塊需要具備獨立并行處理數(shù)據(jù)的特征,從而降低因數(shù)據(jù)包長度的差異導致的流水線中斷的情況發(fā)生。

在數(shù)據(jù)存儲模塊中,不同的數(shù)據(jù)包依靠數(shù)據(jù)包的起始地址及數(shù)據(jù)包長度進行區(qū)分。在數(shù)據(jù)發(fā)射模塊中,需要支持數(shù)據(jù)讀取的起始地址和長度可以動態(tài)配置。因此,構建了圖5所示的數(shù)據(jù)發(fā)射模塊的基本結構。

起始寄存器用于存儲數(shù)據(jù)包的起始地址(基地址),可配置計數(shù)器用于產(chǎn)生當前數(shù)據(jù)包中數(shù)據(jù)的偏移地址,通過加法器將基地址與偏移地址相加可以得到當前送往可重構陣列的數(shù)據(jù)地址。配置控制模塊用于讀取數(shù)據(jù)包包頭并對包頭進行解析,得到當前數(shù)據(jù)包的起始地址及長度,以實現(xiàn)對起始寄存器及可配置寄存器的配置。同時,配置控制模塊也會產(chǎn)生數(shù)據(jù)存儲模塊的讀使能,與數(shù)據(jù)地址相配合,從數(shù)據(jù)存儲模塊中讀取相應的數(shù)據(jù)并送入可重構陣列中相應的位置。

為了確保數(shù)據(jù)包的完整性以及數(shù)據(jù)包在數(shù)據(jù)存儲模塊中存儲的齊整性,本文構建了基于任務映射的數(shù)據(jù)包索引機制,并在多發(fā)射結構中增加了共享的數(shù)據(jù)包索引列表,用于實現(xiàn)對數(shù)據(jù)包的索引。為了對數(shù)據(jù)包進行區(qū)分,本文構建了基于任務號及數(shù)據(jù)包包號的數(shù)據(jù)索引列表,其格式定義如圖6所示。

為便于存儲,本文將數(shù)據(jù)包索引列表定義為32 bit。其中第28到31 bit代表任務編號,用于對不同的任務進行區(qū)分,共4 bit,能夠支持最大16個任務;第26到27 bit為保留字段;第20到25 bit為數(shù)據(jù)包包號,用于區(qū)分同一任務中的不同數(shù)據(jù)包,共6 bit,因此單任務能夠支持最大64個數(shù)據(jù)包;對于網(wǎng)絡數(shù)據(jù)包而言,其長度在64~1 518 B范圍,因此定義1 518 B為單個數(shù)據(jù)包的最大長度,則可以采用9 bit表示單個數(shù)據(jù)包的長度,最大支持2 048 B的數(shù)據(jù);由于本文采用多路并行結構設計數(shù)據(jù)發(fā)射模塊,在數(shù)據(jù)存儲模塊中應至少能夠容納多組最大長度的數(shù)據(jù)包,因此本文將起始地址長度定義為11 bit,從而滿足應用需求。

2.3 數(shù)據(jù)多發(fā)射接口電路設計

數(shù)據(jù)輸入接口電路結構如圖7所示。上位機將待加解密應用分解為不同的任務,并對每個任務中的數(shù)據(jù)進行劃分,劃分為不同長度的數(shù)據(jù)包。根據(jù)數(shù)據(jù)包索引列表格式建立數(shù)據(jù)包索引列表,將數(shù)據(jù)包存入數(shù)據(jù)存儲模塊中的相應地址。當應用被確定后,各數(shù)據(jù)包的起始地址即被確定,為了盡可能減少存儲資源消耗,采用數(shù)據(jù)覆蓋的方式在數(shù)據(jù)存儲模塊中對數(shù)據(jù)包進行存儲,當某一數(shù)據(jù)包完成運算后,其所占用的存儲資源即被釋放,可以在相應存儲資源上進行覆蓋存儲。這一過程主要由上位機實現(xiàn),通過對數(shù)據(jù)包運算過程的規(guī)劃,實現(xiàn)數(shù)據(jù)的無沖突讀寫。

輸入數(shù)據(jù)接口的工作流程如下:

(1)數(shù)據(jù)發(fā)射模塊從數(shù)據(jù)包索引列表中分別讀取數(shù)據(jù)包索引,并解析數(shù)據(jù)包索引中的數(shù)據(jù)包起始地址及長度,將數(shù)據(jù)包起始地址寫入起始寄存器,并將可配置計數(shù)器的溢出值設置為數(shù)據(jù)包長度;

(2)數(shù)據(jù)發(fā)射模塊生成數(shù)據(jù)包的讀地址及讀使能,并將相應信號送至數(shù)據(jù)存儲模塊;

(3)數(shù)據(jù)存儲模塊依據(jù)地址及讀使能,將相應數(shù)據(jù)取出并輸出至粗粒度可重構陣列的對應位置,同時,配置控制模塊生成相應的寫使能;

(4)當數(shù)據(jù)發(fā)射模塊中可配置計數(shù)器產(chǎn)生溢出時,生成溢出信號并傳遞至配置控制模塊,配置控制模塊按順序從數(shù)據(jù)包索引列表中讀取數(shù)據(jù)包索引,繼續(xù)進行運算。

輸入數(shù)據(jù)接口的工作流程確保了輸入數(shù)據(jù)接口能正確地實現(xiàn)數(shù)據(jù)包的解析、數(shù)據(jù)的讀取及發(fā)射,確保了粗粒度可重構陣列中流水線的連續(xù)正確運轉。

3 實現(xiàn)性能比較

本設計采用Verilog硬件描述語言對分組密碼算法進行RTL級描述,利用QuartusⅡ9.0軟件工具對設計進行時序仿真,并選用65 nm CMOS工藝標準單元庫邏輯綜合獲得硬件資源代價。驗證環(huán)境使用Synopsys公司的DC(Design Compiler)邏輯綜合工具,它可以將硬件設計代碼轉換為門級網(wǎng)表,并且能夠映射為特定工藝下的標準單元。為保證工作穩(wěn)定性,將RMPA的工作頻率設置為350 MHz,根據(jù)仿真綜合結果,為更加全面地評估RMPA的實現(xiàn)性能,本文選取典型分組密碼算法AES進行分析。RMPA與其他可重構結構性能對比情況如表1所示。其中RCBCP[5]和Cryptonite[8]為專用指令密碼處理器,Celator[9]、RCPA[10]和S-RCCPA[11]為可重構陣列密碼處理結構。由于各處理結構采用的工藝有較大差異,因此將各結構的面積和吞吐率均按照65 nm CMOS工藝換算并進行比較。

結果表明,RMPA多發(fā)射結構可以高效處理AES分組密碼算法,且吞吐率明顯高于其他專用指令處理器。與Celator和BCORE等其他可重構陣列結構相比較,本結構對分組密碼算法的吞吐率仍處于優(yōu)勢。

4 結論

為充分挖掘分組密碼在可重構陣列中的流水及并行特性,本論文提出了一種面向分組密碼的可重構多發(fā)射流水處理架構RMPA。在65 nm CMOS工藝下對RMPA進行了邏輯綜合和功能仿真,分析了AES算法在該架構下的加密性能,其單發(fā)射/多發(fā)射吞吐率分別達到了0.9 Gb/s和3.19 Gb/s。相比其他密碼處理器,本架構吞吐率高,有一定的性能優(yōu)勢,具有更好的應用前景。下一步將根據(jù)需求對數(shù)據(jù)的多收集機制進行研究,并采用多種分組密碼算法進行分析比較,完善該架構體系。