來源:cnBeta

Speed Select Technology 是英特爾推出的一套電源管理解決方案,特點(diǎn)是能夠根據(jù)用戶工作負(fù)載而調(diào)節(jié)頻率和管理內(nèi)核優(yōu)先級(jí),以達(dá)成性能與效率的雙贏。尷尬的是,正如英特爾自家工程師所觀察到的那樣,在啟用了該模式的基準(zhǔn)測試中,SST 竟然可能導(dǎo)致超過 10% 的性能下降。盡管未說明對實(shí)際工作負(fù)載的影響有多大,但此事還是引發(fā)了相當(dāng)高的關(guān)注。

資料圖(來自:Intel 官網(wǎng))

工程師解釋稱,問題源于 Linux PCI 接口導(dǎo)致的延遲,因其在映射期間搜索了連接到系統(tǒng)的數(shù)百個(gè) PCI 設(shè)備。

雖然難以理解這里為何設(shè)計(jì)數(shù)百個(gè) PCI 設(shè)備,但英特爾 SST 確實(shí)是一套相當(dāng)復(fù)雜的解決方案,并且僅可在基于至強(qiáng)處理器的平臺(tái)上使用(主流消費(fèi)級(jí)酷睿產(chǎn)品線與之無緣)。

在找到問題根源之后,英特爾已承諾將很快通過固件更新的形式進(jìn)行修復(fù)。打補(bǔ)丁的原理也相當(dāng)簡單,即利用緩存數(shù)據(jù)來提速搜索過程。

以下是 Linux 內(nèi)核郵件公告(LKML)中的消息摘要:

我們觀察到一些高性能基準(zhǔn)測試在內(nèi)核中耗費(fèi)了更多的時(shí)間,具體取決于它們正在執(zhí)行的 CPU 數(shù)據(jù)包,且可能導(dǎo)致超過 10% 的顯著差異。

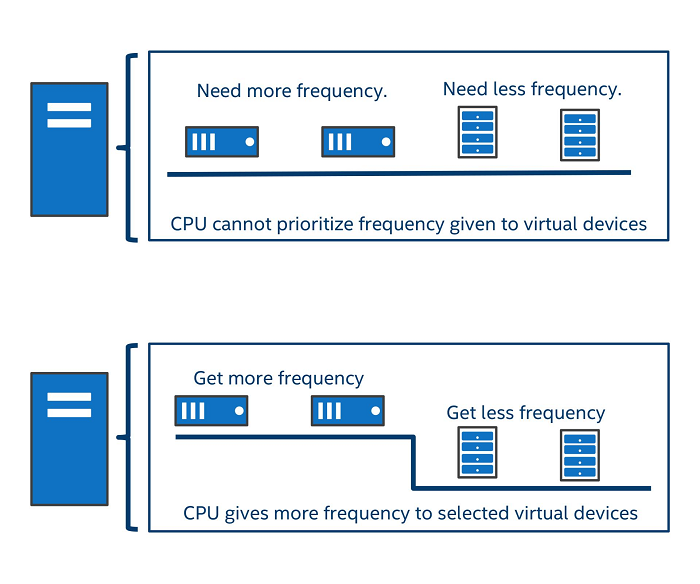

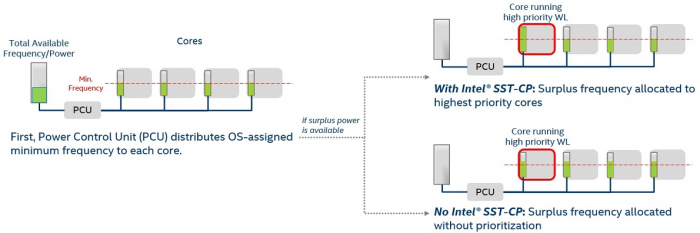

SST 本該提升這些基準(zhǔn)測試的服務(wù)優(yōu)先級(jí),以帶來更高的并行運(yùn)行線程效能,但這種服務(wù)級(jí)別的變動(dòng)又導(dǎo)致了需要訪問 Intel Speed Select PCI 設(shè)備的 MMIO 區(qū)域。

1 - Intel SST - 概述(via)

這種從 CPU 到 PCI 設(shè)備實(shí)例的映射,使用了標(biāo)準(zhǔn)的 Linux PCI 接口 —— 即 pci_get_domain_bus_and_slot() 。

此函數(shù)執(zhí)行抵達(dá) PCI 設(shè)備的線性搜索,但由于測試平臺(tái)上擁有 100 多個(gè) PCI 設(shè)備,結(jié)果導(dǎo)致基準(zhǔn)測試的快速路徑代價(jià)異常高昂。

2 - Inter SST - 設(shè)置(via)

由于這里的 PCI 設(shè)備和功能都是相對固定的,因而 Intel SST 能夠在實(shí)際執(zhí)行時(shí)緩存 CPU 到 PCI 的設(shè)備信息,從而在再次訪問時(shí)顯著提升相關(guān)基準(zhǔn)測試的性能。

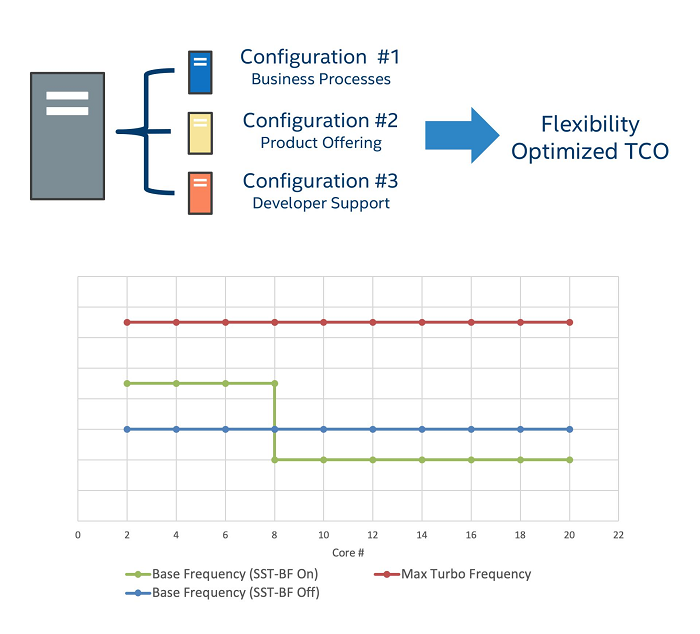

據(jù)悉,英特爾在 2019 年的 Cascade Lake 至強(qiáng)處理器平臺(tái)上隆重介紹了非常通用的 SST 技術(shù),并且提供了包括設(shè)置核心優(yōu)先級(jí)、基礎(chǔ)始終速率等在內(nèi)的多種選項(xiàng)。

不過正如上文所述,SST 功能需要在固件中實(shí)現(xiàn)、并由處理器的電源控制單元(PCU)來執(zhí)行。至于更多細(xì)節(jié),還請移步至英特爾官網(wǎng)(傳送門)查看。